CMOS 2 input NAND gate circuit 및 stick diagram

NAND gate는 parallel로 연결된 PMOS 2개와 series로 연결된 NMOS 2개가 dual형태로 연결되어 있고, 2개의 input인 A, B가

$V_{out}=\overline {AB}$

라는 수식으로 표현되는 CMOS 회로이다. 이에 대한 stick diagram은 아래와 같다.

Input A, B를 가진 pMOS gate 모두가 VDD, Vout과 연결되어 있도록 metal contact을 한다. 또한 Input A를 가진 nMOS gate를 GND와 contact하고, input B를 가진 nMOS gate는 Vout과 연결되도록 contact한다.

Layout 및 추출된 netlist

앞서 CMOS layout 설계의 기준이 된다고 언급하였던 Unit Inverter와 size 비율을 같게 하기 위해 pMOS size : nMOS size = 2 : 2의 조건을 만족하도록 설계했으며, 이에 대한 layout은 위와 같다. pMOS의 경우 Magic 상에서 8*4이고 nMOS 역시 8*4를 만족한다. 이외의 contact과 기타 layer들은 4*4를 기본으로 하여 설계했다. 각각의 Layer들이 어떤 역할을 하는지는 https://hongdoh.tistory.com/2?category=791988 게시물을 참고하면 된다.

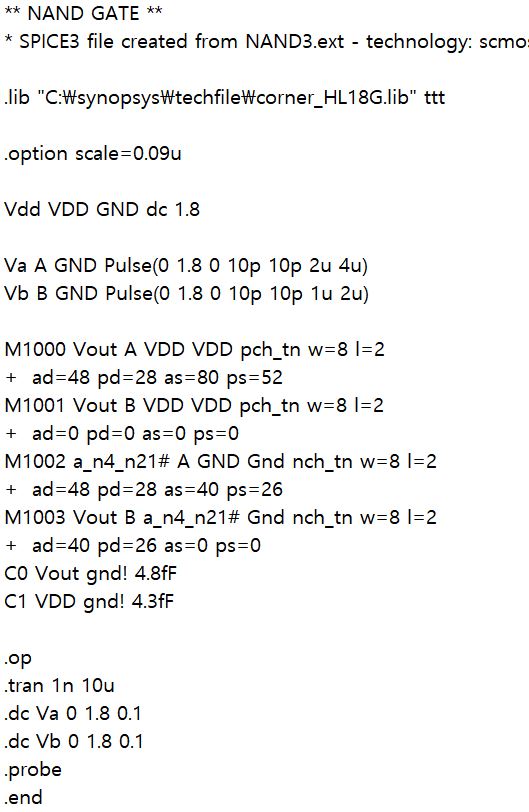

위의 layout에서 netlist를 추출한 결과는 다음과 같다.

Input A, B를 어떻게 조합하는지에 따라 Vout 값이 달라지기 때문에, 전체 4가지의 경우를 모두 simulation하고자 Va와 Vb를 Pulse파로 할당하였다. Va의 경우 T = 4us인 Pulse파를, Vb의 경우 T = 2us인 Pulse파를 인가하였고, 1ns 단위로 10us까지 transient simulation을 수행하도록 operation point를 설정하였다. DC simulation의 경우 Va와 Va 모두 0부터 1.8V까지 0.1V 간격으로 증가시키라는 코드를 입력했다.

HSPICE를 이용한 2 input NAND simulation

1) Transient simulation

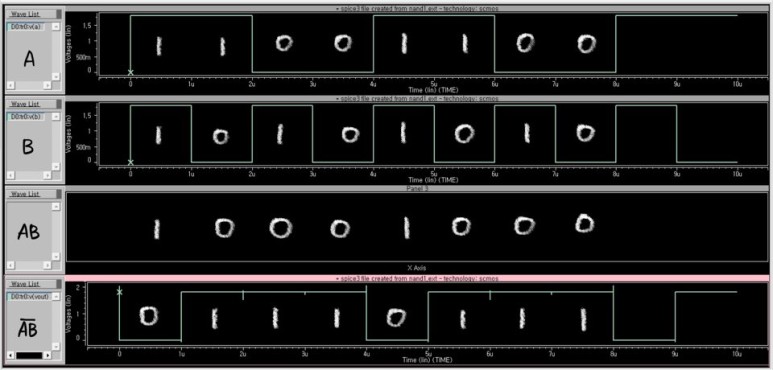

첫번째의 빨간색 Pulse파가 input A, 두번째의 주황색 Pulse파가 input B, 세번째의 노란색 Pulse파가 Vout에 대한 파형이다. 우선 각각 파형에 대한 자세한 설명은 아래와 같다.

Input A가 1 1 0 0 1 1 0 0 1 1의 순서로 2us씩 High와 Low의 값을 번갈아 가질 때, input B는 1 0 1 0 1 0 1 0 1 0의 순서로 1us씩 High와 Low의 값을 번갈아 가진다. 이 때 AB의 값을 연산하면 1 0 0 0 1 0 0 0 1 0 과 같고 (해당 연산 결과는 따로 만들지 않았기 때문에 비어있는 Panel을 이용하였다), 최종 Vout 값인 AB bar는 0 1 1 1 0 1 1 1 0 1의 값을 보이게 된다.

위의 2개의 simulation 결과 중 Vout을 보면 Va와 Vb의 edge가 겹칠때에 voltage가 튀는데, 이는 Pulse파의 주기 조절을 통해 일부 보완 가능하다. 주기 조절 이후에도 voltage가 튄다면 추가적으로 capacitor 값 조절을 통해 해결하도록 한다. 하단의 사진 중 오른쪽 사진의 경우 Va는 T = 14us, Vb는 T = 10us, C0 = 30fF, C1 = 60fF로 수정한 후 30us동안 transient simulation을 수행하도록 했다. 그 결과 전압이 거의 튀지 않는 Pulse파의 형태가 된 것을 확인할 수 있다.

2) DC simulation

DC simulation은 Va가 linear하고 Vb = 0인 switch0의 경우와, Va = 0이고 Vb가 linear한 switch1의 경우가 나온다. 2가지의 경우 모두 simulation의 결과가 같은 모습을 하고 있기 때문에 switch0의 경우만을 첨부하였다. 이 때 Va 값과 무관하게 Vb = 0이기 때문에 Vout은 항상 High, 즉 Vout = 1.8V의 값을 가지게 된다.

CMOS 2 input NAND gate 설계 및 HSPICE를 이용한 simulation 검증은 이렇게 끝이 났으며, 다음은 NOR gate에 대한 설계 과정을 다룰 것이다.

현 게시물을 포함하여 앞으로 작성할 모든 게시물은 본인이 직접 찾아보고 공부하며 정리한 내용을 적은 것이므로, 약간의 오류가 있을 수 있다. 이에 대한 지적과 기타 질문 사항에 대한 댓글은 언제든 환영이다. 해당 카테고리의 게시물은 네이버 블로그와 동일하게 업로드된다. (제 허가가 없는 한 무단으로 수정 및 사용하지 말아주세요)

'홍도의 전공지식 > VLSI 설계 및 프로젝트 실습' 카테고리의 다른 글

| [Magic / HSPICE] Magic tool을 이용한 2 input NOR gate 디자인 (0) | 2020.07.28 |

|---|---|

| [Magic / HSPICE] Magic tool을 이용한 Unit Inverter layout 디자인 (2) - 실습 (0) | 2020.07.21 |

| [Magic / HSPICE] Magic tool을 이용한 Unit Inverter layout 디자인 (1) - 이론 (1) | 2020.07.18 |

댓글