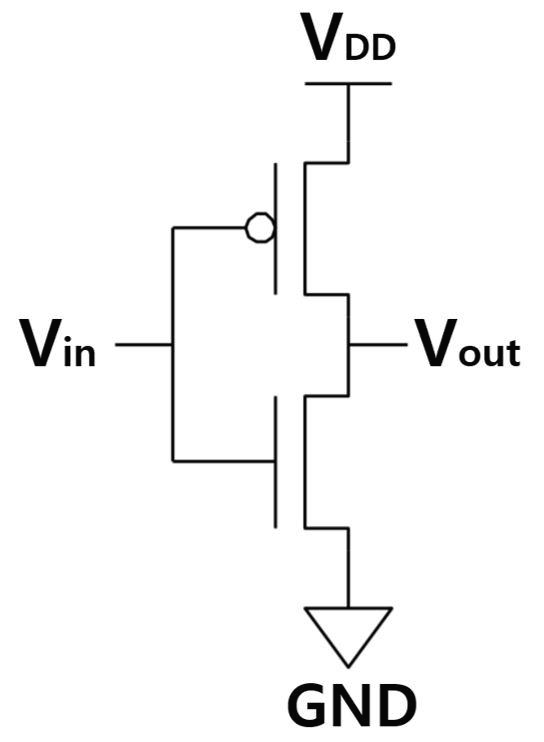

CMOS Unit Inverter의 Stick diagram

Layout 설계를 위해서는 stick diagram을 먼저 그려보는 것을 추천한다. 회로도만을 보고는 바로 tool에서 설계를 하기가 어렵기 때문이다. 대신 Stick diagram을 그릴 때 각 MOSFET의 source, drain이 올바르게 연결되었는지, gate를 공유하는 Transistor끼리 polysilicon이 연결되었는지를 필수적으로 확인해야한다.

Stick diagram을 그릴 때에는 어떤 layer를 그리느냐에 따라 색을 달리 한다. n diffusion은 초록색, p diffusion은 주황색, polysilicon은 빨간색, Metal의 경우는 파란색을 쓰며, contact이 필요할 경우 검은색 X 표시를 한다. 또한 input과 output은 직접 표기해주며, VDD와 GND의 경우는 주로 metal을 이용한다.

위의 사진은 CMOS Unit Inverter를 stick diagram으로 다시 그린 것이다. nMOS의 경우, gate는 빨간색 polysilicon으로 연결되어 있고, source는 VDD, drain은 Vout과 연결되어 있는 것을 볼 수 있다. pMOS의 gate 역시 빨간색 polysilicon을 공유하고 있고, source는 GND, drain은 Vout과 연결되어 있다.

Stick diagram은 그리는 사람에 따라서, 혹은 회로의 모양에 따라서 여러 가지 형태가 나올 수 있다. 회로가 복잡해질수록 형태는 다양해지며, 본인이 설계하기 가장 쉬운 형태를 그려서 이용하면 된다.

Magic tool을 이용한 Layout 설계

앞에서 stick diagram을 먼저 그렸으므로, Magic을 이용하여 stick diagram과 동일한 형태로 설계를 한다. 앞서 말했듯 각각의 layer들은 서로 독립적이므로 어떤 layer를 먼저 깔아줄지에 대한 순서는 중요하지 않다.

사실 layout을 설계할 때는 design rule을 고려하여야 한다. 하지만 현재의 CMOS Unit Inverter를 포함하여 앞으로 이 카테고리에 게재할 layout들은 ①Magic tool에서 Design rule error가 발생하지 않으며, ②기본적인 동작이 구현된다는 단 2가지 조건만을 만족한 것들이다.

첫번째 게시물에 설명하였듯, pMOS size : nMOS size = 2 : 1의 조건을 만족하는 layout은 위와 같다. 참고로 pMOS의 경우 8*4이고 nMOS는 4*4를 만족한다. 이외의 contact과 기타 layer들도 4*4를 유지하며 설계하려했다.

Magic을 이용함에 있어서 layout 설계 과정은 별도로 설명할 것이 없기 때문에 설명은 사진으로 대체하며, 완성이 되었을 경우 저장 후에 netlist를 추출한다.

CMOS Unit Inverter HSPICE netlist

필자의 설계 목표는 netlist 추출시 나오는 기생 Capacitor의 개수를 최소화하는 것이었다. 비교군이 없어서 추출된 netlist의 capacitor가 최소 개수인지는 알 수 없지만, layout의 시행착오를 겪다보면 어느 정도의 개수에 수렴하게 된다. 또한 size 조건을 충족시키고, design rule을 만족하는 올바른 layout일수록 추출한 netlist에서 capacitor 갯수가 적어지는 것을 확인할 수 있다. 그 중에 가장 최소 값을 기준으로 삼는다.

공정 라이브러리는 Magnachip 0.18um를 기준으로 했고, process corner는 ttt로 설정하였다. VDD는 1.8V를 인가하였고, 여기까지의 설정값들은 앞으로 설계할 회로들에도 똑같이 적용할 예정이다.

CMOS Unit Inverter의 가장 기본적 특성인 Input 전압이 inverting 되는 것을 확인하기 위해 Vin에는 T=2us인 Pulse파를 넣어주었다. 기생 Capacitor의 값은 따로 수정하지 않았고, 최하단 문단에 transient simulation은 1ns 단위로 10us동안 반복하며, DC simulation은 Vin 전압을 0V부터 1.8V까지 0.1V단위로 증가시키라는 코드를 입력했다.

CMOS Unit Inverter Simulation 결과

1) Transient Simulation Result

위의 빨간색 파형이 T= 2us인 Vin Pulse이고, 아래의 주황색 파형이 Vout이다. 입력 값이 반전되어 출력되는 것을 확인할 수 있다. 다만 1us 단위로 Low에서 High로 바뀌는 시점에서는 Vout의 값이 조금씩 튀는데, 이러한 현상은 Capacitor를 적절한 값으로 조절하지 않아서 발생한다. 이와 관련해서는 이후에 다른 회로를 설계하며 자세하게 다시 다룰 예정이다.

2) DC Simulation Result

초록색의 linear한 파형이 Vin이고, 노란색의 곡선 파형이 Vout이다. DC simulation의 경우 netlist에서 작성했던 0.1V 간격이 아닌, 1uV 간격으로 다시 simulation을 돌린 것이 위의 사진인데, 0.1V는 간격이 크다고 판단되어 작은 간격으로 재실행한 것이며 결과의 차이는 없다.

위의 사진이 기존의 netlist에서 작성한 것과 같이 0.1V씩 Vin을 증가시켜 나온 simulation 결과인데, 1uV 간격과 달리 Vout의 파형이 매끄럽지 않고 여러개의 짧은 직선으로 이어진 듯한 형태를 볼 수 있다. 아래의 사진은 두 개의 간격에 대한 파형의 일부를 확대하여 비교한 것인데, 왼쪽은 0.1V 간격, 오른쪽은 1uV 간격의 파형이다. 매끄러움에 있어서 확연한 차이가 있음을 알 수 있다.

Transient Simulation의 결과와 마찬가지로 Vin이 Low일 때 Vout은 High로 나오고, Vin이 High일 때 Vout이 Low로 나온다. 또한 1.8V의 중앙값에 가까운 0.894V에서 Vin과 Vout의 크기가 같게 나오는 것을 point를 통해 알 수 있다. 이론 상으로는 정중앙인 Vin = 0.9V에서 Vout 역시 0.9V가 되어야 하지만, 기생 capacitor와 layout 상의 contact 등을 고려했을 때 약간의 오차가 발생할 수 있다.

CMOS Unit Inverter 설계는 이렇게 끝이 났으며, ttt, fff, sss 등의 process corner 등에 대한 별도의 설명은 나중에 VLSI 설계 실습이 아닌 개념 위주의 설명 게시물을 쓰게 된다면 그 때 작성할 예정이다.

현 게시물을 포함하여 앞으로 작성할 모든 게시물은 본인이 직접 찾아보고 공부하며 정리한 내용을 적은 것이므로, 약간의 오류가 있을 수 있다. 이에 대한 지적과 기타 질문 사항에 대한 댓글은 언제든 환영이다.

(대신 제 허가가 없는 한 갖다쓰지 말아주세요)

몇몇 사진과 글들은 Pearson 출판사에서 출판하고, Neil Weste와 David Money Harris가 집필한 "Integrated Circuit Design(CMOS VLSI Design) 4th edition"을 기반으로 한다. 이 뿐만 아니라 전공 교수님께서 설명해주신 내용과 강의노트를 참고하여 작성하였다.

다음 게시물은 NAND, NOR, AND, OR 등의 기본적인 연산 gate에 대해 다룰 것이다.

'홍도의 전공지식 > VLSI 설계 및 프로젝트 실습' 카테고리의 다른 글

| [Magic / HSPICE] Magic tool을 이용한 2 input NOR gate 디자인 (0) | 2020.07.28 |

|---|---|

| [Magic / HSPICE] Magic tool을 이용한 2 input NAND gate 디자인 (0) | 2020.07.22 |

| [Magic / HSPICE] Magic tool을 이용한 Unit Inverter layout 디자인 (1) - 이론 (1) | 2020.07.18 |

댓글